OP Amp는 Operational Amplifier의 약자로 연산 증폭기이다.

OP Amp는 두 개의 차동 입력과 보통의 경우 한 개의 단일 출력을 갖는 전압 증폭기이다.

OP Amp는 회로 구성에 따라서 덧셈, 뺄셈, 미분, 적분과 같은 수학적 연산을 설계할 수 있다.

회로설계에 있어서 OP Amp의 특징을 큰 들에서 개괄적으로 말할 때 OP Amp로 입력되는 입력 임피던스는 거의 무한대와 가깝거나 아주 높은 상태라고 하며 출력되는 출력 임피던스는 거의 0에 가깝거나 아주 낮은 상태라고 말한다.

OP Amp를 응용한 다양한 회로가 존재하지만 다양한 회로를 설계하기 앞서 회로설계에서 OP Amp의 데이터시트를 통해 실질적으로 필요한 사항을 설명하고자 한다.

아래 사진은 TI사의 OPA317의 요약된 특징이 나타나있는 데이터시트의 Features이다.

OPA371의 구동전압은 Supply Voltage를 통해 1.8V에서 5.5V 범위인 것을 확인할 수 있다.

microPackages는 OPA317의 IC 패키지를 나타내며 PCB Layout의 풋프린트와 연관되어 있다.

Low Offset Voltage는 OPA317이 가진 Offset Voltage를 나타낸다.

OPA317은 통상적으로 20uV Offset Voltage를 가진다.

Offset Voltage가 0V에 가까운 OP Amp를 선정하는 것을 권장한다.

Gain Bandwidth는 OP Amp로 증폭시킬 수 있는 최대 입력 신호의 주파수가 300 kHz임을 말해준다.

300 kHz 이상의 신호를 입력시킬 경우 OPA317로는 의도한 설계로 증폭시킬 수 없다.

Rail-to-Rail Input/Output은 입/출력되는 신호가 OP Amp의 공급 전압 범위 이내에서 가능함을 말해준다.

OPA317은 내부에 EMI와 RFI를 저잠시킬 수 있는 필터링 회로가 내장되어 있다.

아래 사진은 OP Amp가 갖는 입력 Offset Voltage의 분포도를 나타낸다.

그래프를 통해서 OP Amp의 입력 Offset Voltage를 확인할 수 있으며 회로설계와 MCU 등을 이용한 ADC 설계 시 검토해야 될 부분이다.

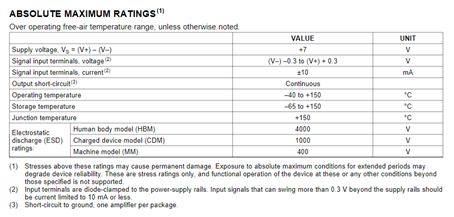

아래 사진은 OPA317의 Absolute Maximum Ratings 데이터이다.

회로설계 시 필수적으로 확인해야 될 사항이다.

Vs인 Supply voltage 항목에 Vs = (V+) - (V-)로 표기되어 있다.

이는 입력되는 주전원 전압의 상대적 차이가 최대 7V를 넘어서면 안 되는 것을 의미한다.

또한 OP Amp의 입력 신호 역시 주전원 전압 범위의 ±0.3V와 ±10mA를 넘어서면 안 되므로 주의해야 된다.

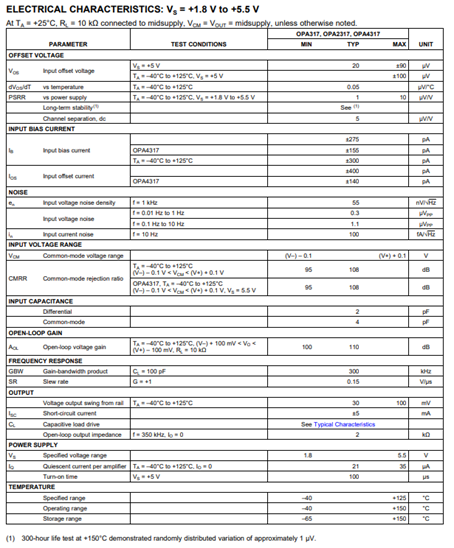

아래 사진은 OPA317의 Electrical Characteristics 데이터이다.

Input Offset Voltage는 통상적으로 20uV로 나타나 있지만 MAX 값은 ±90uV이고 온도 조건이 더해질 경우 MAX 값이 ±100uV로 크게 증가한다.

이는 입력 신호에 Offset Voltage 신호가 실리게 되면 최종 출력에는 Offset Voltage 신호가 증폭되어 출력 신호에 나타나므로 확인해야 될 부분이다.

OP Amp를 이용하여 Common-mode로 동작시킬 때의 입력 신호는 OP Amp로 공급되는 전원 전압 범위를 넘어서면 안 된다.

데이터시트에서 최저 전압과 최고 전압보다 0.1 만큼 허용이 가능하지만 가급적 전원 전압 범위 안으로 설계하는 것을 권장한다.

주파수 응답 특성으로 부하 캐패시턴스가 100pF 일 때 최대 300 kHz 이하의 신호를 증폭시킬 수 있어 이보다 높은 신호는 흡사 Low-Pass Filter와 같이 필터링된다.

Slew rate는 입력되는 신호의 변화가 실제 출력에 나타나는 시간에 따른 변화율을 나타낸다.

OP Amp의 증폭 이득이 1일 때 0.15V/us로 1V의 신호를 입력할 때에 실제 출력이 1V가 나타나는 시간은 다른 요소는 고려하지 않고 Slew rate만 놓고 계산할 때에 약 6.67us가 걸린다.

출력에 대한 사항으로는 OP Amp로 공급되는 전원 전압 범위에서 통상 30mV로 스윙한다.

최악의 경우 100mV까지 스윙할 수 있으니 설계 시 이에 대한 고려가 반드시 필요하며 출력 단락 시 ±5mA의 출력 전류가 발생한다.

Turn-on time은 OPA317이 구동전압을 인가받아 정상적인 동작을 수행할 수 있는 시간이다.

통상 100us이므로 MCU를 통해 ADC 처리할 때 100us이후로 데이터 처리를 해야 된다.

'[Circuit Design] > OP Amp' 카테고리의 다른 글

| Comparator(비교기) 설계 (0) | 2021.09.06 |

|---|---|

| Differential Amplifier(차동 증폭기) 설계 (0) | 2021.09.03 |

| Non-Inverting Amplifier(비반전 증폭기) 설계 (0) | 2021.08.31 |

| Inverting Amplifier(반전 증폭기) 설계 (0) | 2021.08.28 |

| Voltage Follower(버퍼) 설계 (0) | 2021.08.22 |

| OP Amp의 Slew Rate 파라미터 (0) | 2021.08.19 |